#### MIL-PRF-38534 CERTIFIED FACILITY

## RAD HARD HIGH VOLTAGE **SYNCHRONOUS** SWITCHING REGULATOR CONTROLLER

# 5055RH SFRIFS

#### FEATURES:

- TECHNOLOGY Space Qualified RH3845 Dice Manufactured using

- Radiation Hardened to 300 Krad(Si) (Method 1019.7 Condition A)

- Neutron Tested to 5E11 n/cm<sup>2</sup> (Method 1017.2)

- High Voltage Operation: Up to 60V Input, and 36V Output

- Programmable Frequency 100-500KHz, or Synchronizable to 600KHz

- 70µA Shutdown Supply Current

TTM Technologies

- Antislope Compensation Current Limit Unaffected by Duty Cycle

- · Reverse Inductor Current Inhibit Improves Efficiency with Light Loads

- **External Compensation** •

- Capable of Driving Standard Power MOSFETs

- Available to DLA SMD 5962F14223

#### DESCRIPTION:

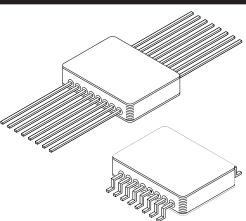

The MSK5055RH is a radiation hardened wide input voltage range step-down synchronous switching regulator controller. The wide input range, programmable output voltage and switching frequency, make these regulators suitable for a wide variety of medium to high power applications. The adjustable operating frequency provides the flexibility to keep the switching noise out of sensitive frequency bands, and when synchronized, can be ganged out of phase with other controllers for reduced noise and component size. The MSK5055RH is hermetically sealed in a 16 pin flatpack, and is available with straight or gull wing leads.

#### **TYPICAL APPLICATIONS**

- POL Applications

- Intermediate Bus Converter

- Satellite System Power Supply

- Step Down Synchronous Regulator

▲ And the Linear Technology logo are registered trademarks and RH3845 is a copyright of Linear Technology Corporation

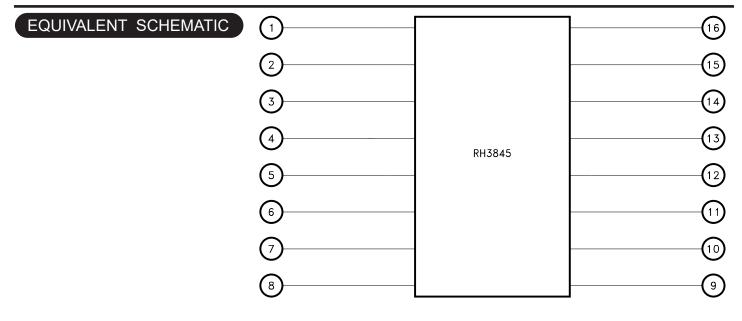

| PIN-OUT INFORMATION |      |    |        |  |  |  |  |

|---------------------|------|----|--------|--|--|--|--|

| 1                   | VIN  | 9  | SENSE- |  |  |  |  |

| 2                   | SHDN | 10 | SENSE+ |  |  |  |  |

| 3                   | CSS  | 11 | PGND   |  |  |  |  |

| 4                   | SGND | 12 | BG     |  |  |  |  |

| 5                   | VFB  | 13 | VCC    |  |  |  |  |

| 6                   | VC   | 14 | SW     |  |  |  |  |

| 7                   | SYNC | 15 | TG     |  |  |  |  |

| 8                   | FSET | 16 | BOOST  |  |  |  |  |

| CASE = ISOLATED     |      |    |        |  |  |  |  |

## ABSOLUTE MAXIMUM RATINGS 1

| VIN    | Input Voltage                            | 65V          |

|--------|------------------------------------------|--------------|

| VBOOST | BOOST Voltage (BOOST)                    | 80V          |

| SW     | Switch Voltage9                          | . 65V to -2V |

|        | Differential Boost Voltage (BOOST TO SW) | 24V          |

| VCC    | Bias Supply Voltage                      | 24V          |

| VSENSE | SENSE+ and SENSE- Voltages               | 40V          |

|        | Differential Sense Voltage               | ±1V          |

|        | SYNC, VC, VFB, CSS and SHDN              | 5V           |

|        | SHDN Pin Currents                        | 1mA          |

| Tld | Lead Temperature Range<br>(10 Seconds) 300°C |

|-----|----------------------------------------------|

| Тѕт | Storage Temperature 13                       |

| ΤJ  | Junction Temperature 150°C                   |

| Тс  | Operating Case Temperature                   |

|     | MSK 5055K/H RH55°C TO +125°C                 |

|     | MSK 5055RH40°C TO +85°C                      |

|     | ESD Rating 1C                                |

|     |                                              |

## ELECTRICAL SPECIFICATIONS

| Demonster                                | Test Conditions                    | 1 11                                   | Group A   | MSK5055K/H RH  |         |                | MSK5055RH |            |         | Unite     |

|------------------------------------------|------------------------------------|----------------------------------------|-----------|----------------|---------|----------------|-----------|------------|---------|-----------|

| Parameter                                |                                    |                                        | Subgroup  | Min.           | Тур.    | Max.           | Min.      | Тур.       | Max.    | Units     |

| VIN Min Start Voltage                    |                                    |                                        | 1, 2, 3   | -              | -       | 7.5            | -         | -          | 7.5     | V         |

|                                          |                                    |                                        | 1, 2, 3   | 3.6            | 3.7     | 4              | 3.6       | 3.7        | 4       | V         |

| VIN UVLO Threshold (Falling)             |                                    | Post 100 Krad(Si)                      | 1         | 3.55           | 3.6     | 4              | 3.55      | 3.6        | 4       | V         |

|                                          |                                    | Post 300 Krad(Si)                      | 1         | 3.45           | 3.5     | 4              | 3.45      | 3.5        | 4       | V         |

| VIN Supply Current (2)                   | VCC ≥                              | 9V                                     | 1         | -              | 130     | -              | -         | 130        | -       | uA        |

| VIN Shutdown Current (2)                 | VSHDN =                            | = 0V                                   | 1, 2, 3   | -              | 65      | -              | -         | 65         | -       | uA        |

| BOOST Supply Current 23                  |                                    |                                        | 1         | -              | 1.6     | -              | -         | 1.6        | -       | mA        |

| VCC Supply Current                       |                                    |                                        | 1         | -              | 4       | 4.5            | -         | 4          | 4.5     | mA        |

|                                          |                                    |                                        | 2, 3      | -              | -       | 5.5            | -         | -          | -       | mA        |

| VCC Current Limit                        |                                    |                                        | 1, 2, 3   | 40             | -       | -              | 40        | -          | -       | mA        |

|                                          | VC = VFB                           |                                        | 1         | 1.214          | 1.233   | 1.250          | 1.214     | 1.233      | 1.250   | V         |

| Error Amp Reference Voltage              |                                    |                                        | 2, 3      | 1.214<br>1.200 | - 1.222 | 1.250<br>1.250 | - 1.200   | -<br>1.222 | - 1.250 | V<br>V    |

|                                          |                                    | Post 100 Krad(Si)<br>Post 300 Krad(Si) | 1         | 1.173          | 1.197   | 1.250          | 1.173     | 1.197      | 1.250   | V         |

| VFB Pin Input Current (2)                | VFB = Y                            |                                        | 1         | -              | 35      | -              | -         | 35         | -       | nA        |

|                                          | VFD -                              | VREF                                   | 1, 2, 3   | - 1.3          | 1.37    | - 1.5          | - 1.3     | 1.37       | - 1.5   | V         |

| SHDN Enable Threshold (Rising)           |                                    | Post 300 Krad(Si)                      | 1, 2, 3   | 1.25           | 1.3     | 1.5            | 1.25      | 1.3        | 1.5     | V         |

| SHDN Threshold Hysteresis (2)            |                                    |                                        | 1         | -              | 125     | -              | -         | 125        | -       | mA        |

|                                          | (VSENSE+) - (VSEN                  | SE-) VFB = 0V                          | 1, 2, 3   | 85             | 109     | 125            | 85        | 109        | 125     | mV        |

| Current Limit Sense Voltage              |                                    | Post 100 Krad(Si)                      | 1, 2, 0   | 80             | 103     | 125            | 80        | 103        | 125     | mV        |

| g-                                       |                                    | Post 300 Krad(Si)                      | 1         | 70             | 92      | 125            | 70        | 92         | 125     | mV        |

| Input Current (ISENSE+) + (ISENSE-) (2)  | VSENSE (CI                         | v) = 0V                                | 1         | -              | 705     | -              | -         | 705        | -       | uA        |

|                                          | Rset = 49.9KΩ                      |                                        | 4         | 270            | 320     | 370            | 260       | 320        | 370     | KHz       |

| Operating Frequency                      |                                    |                                        | 5, 6      | 240            | -       | 390            | -         | -          | -       | KHz       |

|                                          |                                    | Post 300 Krad(Si)                      | 4         | 260            | 320     | 370            | 260       | 320        | 370     | KHz       |

| Programmable Frequency Range             | Fsw ≤ 100kHz at<br>Fsw ≤ 500kHz at |                                        | 7, 8a, 8b | Pass           | -       | -              | Pass      | -          | -       | Pass/Fail |

| External Sync Frequency Range            | 100kHz ≤ Fsyn                      | c ≤ 600kHz                             | 7, 8a, 8b | Pass           | -       | -              | Pass      | -          | -       | Pass/Fail |

| Sync Voltage Threshold                   |                                    |                                        | 1, 2, 3   | -              | 1.4     | 2              | -         | 1.4        | 2       | V         |

| Soft-Start Capacitor Control Current (2) |                                    |                                        | 1         | -              | 11      | -              | -         | 11         | -       | uA        |

| Error Amp Transconductance (2)           |                                    |                                        | 1, 2, 3   | -              | 450     | -              | -         | 450        | -       | uS        |

| Error Amp DC Voltage Gain (2)            |                                    |                                        | 1         | -              | 62      | -              | -         | 62         | -       | dB        |

| Error Amp Sink/Source Current (2)        |                                    |                                        | 1         | -              | ±40     | -              | -         | ±40        | -       | uA        |

| TG, BG Drive On Voltage (2)(4)           | CLOAD = 3                          | 300pF                                  | 1         | -              | 8.5     | -              | -         | 8.5        | -       | V         |

| TG, BG Drive Off Voltage (2)             | CLOAD = 3                          | 300pF                                  | 1         | -              | 0       | -              | -         | 0          | -       | V         |

| TG, BG Drive Rise/Fall Time 2            | 10% to 90% or<br>CLOAD = 3         | 90% to 10%                             | 4         | -              | 60      | -              | -         | 60         | -       | nS        |

| Minimum TG Off Time                      |                                    |                                        | 4, 5, 6   | -              | 290     | 400            | -         | 290        | 400     | nS        |

| Minimum TG On Time                       |                                    |                                        | 4, 5, 6   | -              | 230     | 500            | -         | 230        | 500     | nS        |

| Gate Drive Nonoverlap Time (2)           | TG Fail to I                       | BG Rise                                | 4         | -              | 250     | -              | -         | 250        | -       | nS        |

|                                          | TG Fail to                         |                                        | 4         | -              | 250     | -              | -         | 250        | -       | nS        |

| Thermal Resistance (2)                   | Junction to Cas                    | se @ 125°C                             | -         | -              | 5.2     | 5.6            | -         | 5.2        | 6.1     | °C/W      |

#### NOTES:

- (1) Unless otherwise specified VIN = 20V, VCC = BOOST = 10V,  $\overline{SHDN} \ge 2V$ , RSET = 49.9K $\Omega$ , SENSE- = SENSE+ = 10V, SGND = PGND = SW = SYNC = 0V.

- ② Guaranteed by design but not tested. Typical parameters are representative of device performance but are for reference only.

- 3 Supply current specification does not include switch drive currents. Actual supply currents will be higher.

- (4) DC measurement of gate drive output "ON" voltage is typically 8.6V. Internal dynamic bootstrap operations yields typical gate "ON" voltages of 9.8V during standard switching operation. Standard operation gate "ON" voltage is not tested but guaranteed by design.

- 5 Industrial grade devices shall be tested to subgroup 1 unless otherwise specified.

- 6 Military grade devices ("H" and "K" suffix) shall be 100% tested to subgroups 1,2,3,4 and 7.

- Subgroup 3,6 and 8 available upon request.

- Subgroup 1,4,7 TC = +25°C

Subgroup 2,5,8a TC = +125°C

Subgroup 3,6,8b TC = -55°C

- 9 The -2V absolute maximum on the SW pin is a transient condition. It is guaranteed by design, but not tested.

- 0 Continuous operation at or above absolute maximum ratings may adversely affect the device performance and/or life cycle.

- 1 Pre and post irradiation limits at 25°C, up to 300 Krad(Si) TID, are identical unless otherwise specified.

- 2 Reference DLA SMD 5962F14223 for electrical specifications for devices purchased as such.

- 13 Internal solder reflow temperature is 180°C, do not exceed.

#### **APPLICATION NOTES**

## DEVICE TYPES (-1, -2)

The MSK5055RH can be ordered to operate in one of two different ways at light load. The different modes are internally configured at the factory and are identified by the "dash number."

| DASH<br>NUMBER | MODE<br>Internal Connection | Reverse Current<br>Mode |

|----------------|-----------------------------|-------------------------|

| -1             | VFB                         | Disabled (DCM)          |

| -2             | VCC                         | Enabled (CCM)           |

Device type "-1" disables the reverse current capability at light loads. This configuration is more efficient than configuration "-2." It allows the inductor current to go discontinuous and the PWM will skip pulses to maintain regulation at light loads. This configuration will have a minimum load current requirement, typically 1mA.

Device type "-2" allows reverse current in the synchronous switch at light loads. This configuration is less efficient at light loads but operations in continuous conduction mode at light loads.

#### **PIN FUNCTIONS**

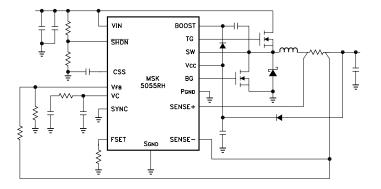

VIN - The VIN pin is the input supply pin for the device, and should be decoupled to SGND with a low ESR capacitor located close to the pin — ( See application circuit for typical values).

VCC - The VCC pin provides access to the internal 8V bias supply for decoupling and optional external sourcing. It is the power supply for most of the internal functions and the MOSFET gate drive. VCC can only source current and may be tied to an external source to improve efficiency and allow for lower voltage operation. If VCC is tied to an external source greater than 6.5V the device will operate with Vin as low as 4V. This configuration reduces power dissipation in the device by bypassing the internal regulator. The VCC pin charges the bootstrapped capacitor through a diode connected to the BOOST pin. In shutdown mode the VCC pin sinks  $20\mu$ A until the pin voltage is discharged to zero volts. Note: When connecting VCC to an external source, the source must be greater than or equal to VCC +1V.

TG - The TG pin is the gate drive for the forward switch, or top N-Channel MOSFET. Be aware of the high speed and large currents here during circuit layout. Keep traces short and as wide as possible to minimize parasitic impedances.

BG - The BG pin is the gate drive for the synchronous rectifier or bottom N-Channel MOSFET. Be aware of the high speed and large currents here during circuit layout. Keep traces short and as wide as possible to minimize parasitic impedances.

PGND - The PGND pin is the high-current ground reference. Connect it directly to the negative side of the VCC decoupling capacitor. Care should be taken to make sure that these currents are not referenced by the SGND pin to avoid injecting noise into the ground reference. SGND - The SGND pin should be connected to the negative side of the output capacitor. Use a common ground plane to minimize impedance, but locate the high current fast switching devices together so their returns remain local and do not corrupt the SGND reference.

SW - The SW pin is the switch node for the device. The source of the top MOSFET (forward switch), the drain for the bottom MOSFET (synchronous rectifier), the inductor, and the BOOST capacitor are all connected to this node. Use short wide trace to minimize the impedance of this node.

$\overrightarrow{SHDN}$  - The  $\overrightarrow{SHDN}$  pin provides a method to disable the device. Pull this pin below 1.35V (nominal) to disable switching. Pull below one  $V_{BE}$  (0.7V nominal) to enter low power shutdown. A resistor divider to VIN can be used to set UVLO using the 1.35V threshold. When not in use, pull the pin up to VIN with a large value resistor. When exceeding the absolute maximum rating of 5V the pin voltage will be clamped at 6V nominal. Limit the current into the pin to less than 1mA to prevent overstress.

BOOST - The BOOST pin provides the supply for the bootstrapped gate drive, and is externally connected to a low ESR ceramic BOOST capacitor. The value of the BOOST capacitor should be at least 50 times greater than the gate capacitance of the top MOSFET. Smaller values may be used, but analysis of the voltage drop is recommended. An external diode connected from VCC to the BOOST pin charges the bootstrap capacitor during the off-time of the main power switch. Locate the VCC and BOOST decoupling capacitors in close proximity to the device.

CSS - The CSS pin is used for soft start. It allows the user to program the rate of change of the output at start-up. The capacitance required for a given output slew rate can be calculated using the following formula:

$CSS = 11\mu A(Tss/1.231V)$

The pin should be left open if not in use.

SENSE<sup>-</sup> - The SENSE<sup>-</sup> pin is the negative input to the current sense amplifier. The sensed inductor current limit is set to 100mV across both SENSE inputs.

RSENSE = 70mV/IOUT(MAX)

Given: IP-P < 0.30 x IOUT(MAX)

SENSE<sup>+</sup> - The SENSE<sup>+</sup> pin is the positive input to the current sense amplifier. The sensed inductor current limit is set to 100mV across both SENSE inputs.

RSENSE = 70 mV/IOUT(MAX)

Given: IP-P < 0.30 x IOUT(MAX)

#### APPLICATION NOTES CONT'D

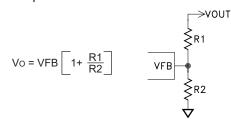

**VFB** - The VFB (Feedback) pin is used to set the output voltage. Use a resistive divider to set the voltage at the VFB pin to 1.231V when the output is at the desired level.

**VC** - The VC pin provides a means to externally compensate the loop response of the controller. VC is the output of the transconductance error amplifier. A capacitor to ground creates a pole in the control loop. A series RC creates a pole zero combination in the control loop. If the VC pin is externally manipulated, use a source impedance of 1K $\Omega$ .

**FSET** - The FSET pin programs the oscillator frequency via a single resistor to ground. The R<sub>SET</sub> resistor must be present even when synchronization mode is used - Use the formula or the table below to select the resistance value for a desired frequency.

| FSW (KHz) |

|-----------|

| 100       |

| 150       |

| 200       |

| 250       |

| 300       |

| 350       |

| 400       |

| 450       |

| 500       |

|           |

RSET(K $\Omega$ )  $\approx 9.55 \text{ x } 10^4 \text{ x } \text{fsW}(\text{KHz})^{(-1.31)}$

**SYNC** - The SYNC pin is the input for synchronization of the internal oscillator to an external clock. Program the internal oscillator to be between 10% and 25% below the external clock. The recommended signal is a square wave of at least 2V in amplitude, a pulse width greater than 1 $\mu$ S, and a rise time of less than 500nS. If the SYNC pin is not used in the application, tie it to SGND.

#### TYPICAL APPLICATION CIRCUIT

#### SELECTING THE SWITCHING FREQUENCY

The MSK5055RH can be set to operate over a frequency range of 100KHz to 500KHz, and is synchronizeable up to 600KHz. There are several factors to consider when selecting the operating frequency including: efficiency, component size, output ripple, application sensitive frequency bands, and the minimum on time of the controller. The output ripple voltage and efficiency will vary with frequency and input voltage. Higher frequencies increase switching losses, but use smaller inductors and/or bulk capacitors saving board space. Lower frequencies reduce switching losses, but increase ripple current and require larger inductors and/or bulk capacitance to achieve the same output ripple voltage.

#### SELECTING THE INPUT CAPACITOR

The input capacitance provides a low impedance source to the input of the regulator. A low impedance is necessary for high speed, high efficiency switching and tight regulation. The input bus sources an average DC current while the input capacitance sources the AC component of the input current. Select the input capacitor based on voltage ripple requirements, RMS current rating and bulk capacitance. Assuming the capacitor ESR is lower than the bus impedance at the switching frequency and above, the ESR will dominate the voltage ripple.

VP-P ≅ IP-P x ESR Given: IP-P = IOUT

The RMS current capability is related to power dissipation capability of the capacitor. Replace the capacitor with one that has a higher rating, or place more capacitors in parallel if more capability is needed. Sharing of ripple current between capacitors will be approximately equal if all of the capacitors are the same type, and preferably from the same lot. The RMS current seen by the input capacitors can be approximated by the following equation:

$\label{eq:RMS} \begin{array}{l} {\sf IRMS} \cong {\sf IOUT} \; x \; SQRT \; (3D^2 - 3D \; {\rm +1}) \\ {\sf Given:} \; D \cong {\sf VOUT}/{\sf VIN} \end{array}$

Parallel ceramic capacitors are required to filter the high frequency components of the switching waveform. Locate the bias supply capacitors close to the VIN and SGND pins on the MSK5055RH. Locate the power input capacitors close to the drain of the forward switch (VIN) and the source of the synchronous rectifier (Power Ground). Use short, wide PCB lands to minimize parasitic impedances.

#### APPLICATION NOTES CONT'D

#### SELECTING THE OUTPUT CAPACITOR

The output capacitor filters the ripple current from the inductor to an acceptable ripple voltage seen by the load. The primary factor in determining voltage ripple is the ESR of the output capacitor. The voltage ripple can be approximated as follows:

The capacitive term of the output voltage ripple lags the ESR term by 90° and can be calculated as follows:

$$VP-P(CAP) = IP-P/(8 \times f \times c)$$

Where:

C = output capacitance in Farads

Select a capacitor or combination of capacitors that can tolerate the worst-case ripple current with sufficient de-rating. When using multiple capacitors in parallel to achieve lower ESR or more bulk capacitance, sharing of ripple current between capacitors will be approximately equal if all of the capacitors are the same type, and preferably from the same lot. Low ESR tantalum capacitors are recommended over aluminum electrolytic capacitors. Use ceramic decoupling capacitors to minimize high frequency noise.

#### COMPENSATING THE LOOP

The feedback loop response can be optimized for the application by adjusting the values of the RC network from the  $V_c$  pin to ground. Analysis is recommended to determine the phase margin and gain margin at the specific input voltage and load conditions of the application. Typically, a single RC network from VC to ground works well. An additional ceramic capacitor from VC to ground may be needed to cancel the zero and prevent high frequency ringing or instability.

#### SELECTING THE INDUCTOR

The important parameters for inductor selection are: its value, volt-second product, saturation and RMS current. To determine the peak current in the inductor add ½ of the p-p ripple current to the desired IOUT(MAX). A typical starting point for peak to peak current ripple is 20% of IOUT(MAX). Use the following equation to determine the RMS current:

IRMS = IDC \* SQRT (

$$1 + (1/3) * (\Delta I / IDC)^2$$

)

Given:

IDC = The DC output current  $\Delta I = \frac{1}{2}$  of the peak to peak ripple current

The minimum inductance value can be calculated as follows:

$$L_{MIN} > V_{OUT} x \frac{2DC_{MAX}-1}{DC_{MAX}} x \frac{R_{SENSE} x 8.33}{f_{SW}}$$

Given:

DC = Duty Cycle = VOUT/VIN

fsw = Switching Frequency

This calculation also accommodates the max ripple/DC requirements for the slope compensation circuit.

The volt-seconds product can be calculated as follows:

Given:

$V_{I}$  = the inductor voltage ( $V_{IN} - V_{O}$ ) dt =  $V_{O}/(V_{IN} \times f_{SW})$

Allow sufficient derating to prevent saturation and/or overstress when selecting the inductor.

#### SELECTING THE MOSFETS

A compromise between conduction loss and transition loss is recommended for the top MOSFET (forward switch). The bottom MOSFET's (synchronous rectifier) power dissipation is dominated by the conduction loss. For highest efficiency, keep the total power dissipation in each switch as low as possible. Conduction loss is a function of RDS(ON), and transition loss is a function of CRSS. The transition losses become more significant as input voltages and switching frequency rise.

Gate charge losses are dissipated in the MSK5055RH gate and drive the gate resistors if used. Gate charge is related to RDS(ON) and transition time. The power dissipated in the MSK5055RH and gate resistors due to gate charge by each MOSFET can be approximated by the following equation:

PD(GATE DRIVE) = QG x VG x FSW

When the VCC pin is not externally bypassed the internal linear regulator will dissipate power according to the following equation:

$PD(REG) \approx (VIN-8) \times ((QG(TOTAL) \times FSW) + 3mA)$

Given: QG = Gate Charge VG = Gate Drive Voltage Fsw = Switching Frequency

Parasitic FET capacitances can couple the negative switch node transients onto the bottom MOSFET gate drive pin of the device, which could exceed the absolute maximum rating for the pin. A Schottky catch diode rated for 1A is recommended connected to ground to protect the pin from these transients.

#### TOTAL DOSE RADIATION TEST PERFORMANCE

Radiation performance curves have been generated for all testing performed by TTM Technologies. These curves show performance trends throughout each test process, and are located in the MSK5055RH radiation test report. The complete test report as available in the RAD HARD PRODUCTS section of the TTM Technologies website.

#### ADDITIONAL APPLICATION INFORMATION

For additional applications information, please reference Linear Technology's  $^{\!\!\!\rm s}$  LT3845 data sheet.

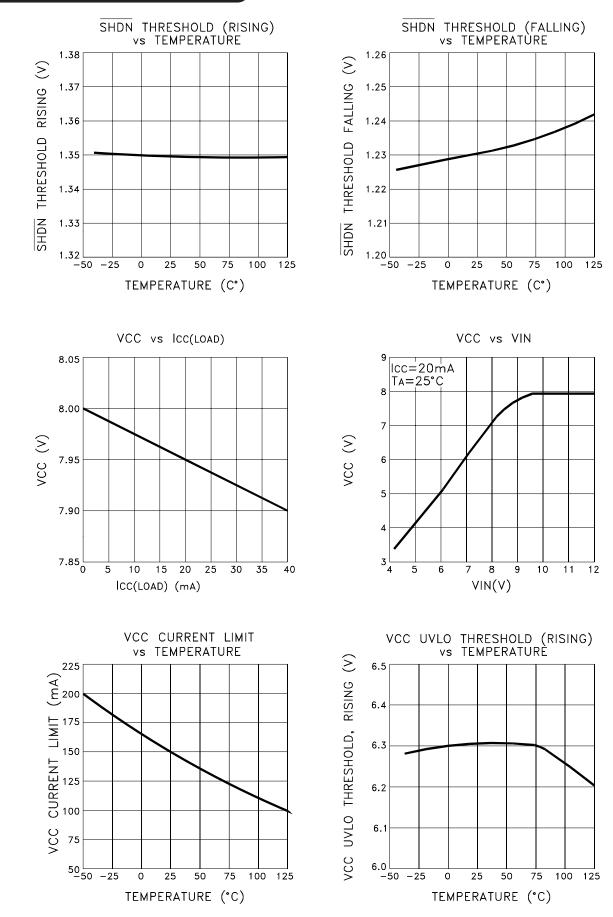

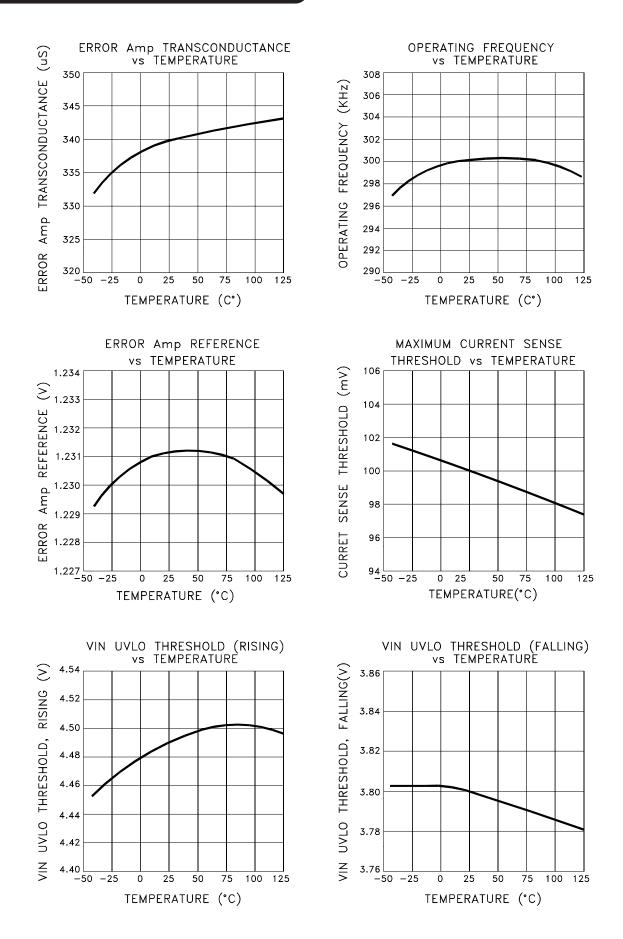

### TYPICAL PERFORMANCE CURVES

#### TYPICAL PERFORMANCE CURVES CONT'D

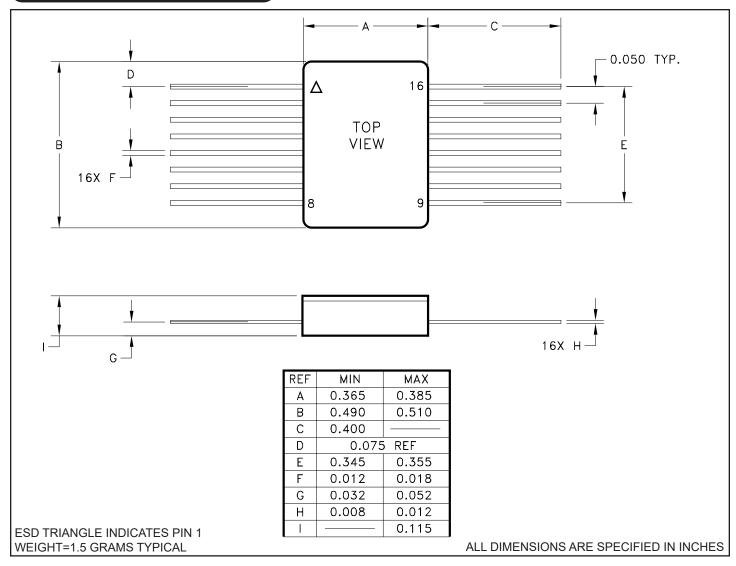

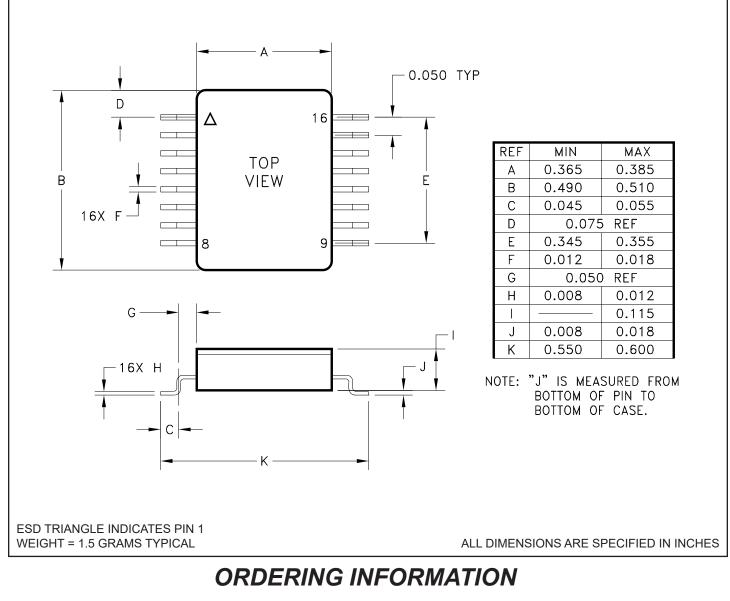

#### MECHANICAL SPECIFICATIONS

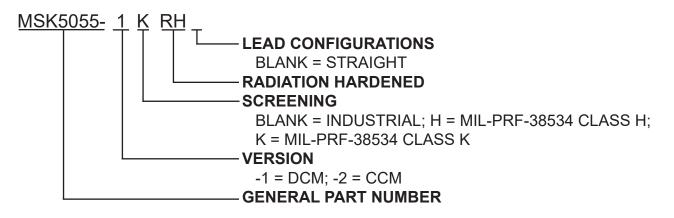

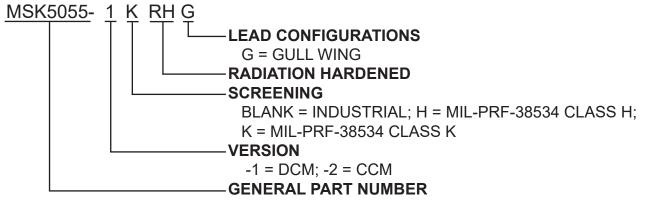

## **ORDERING INFORMATION**

The above example is a DCM, Class K regulator controller with straight leads.

NOTE: See DLA SMD 5962F14223 for DLA part number options.

#### MECHANICAL SPECIFICATIONS

The above example is a DCM, Class K regulator controller with gull wing formed leads.

NOTE: See DLA SMD 5962F14223 for DLA part number options.

## **REVISION HISTORY**

| REV | STATUS   | DATE  | DESCRIPTION                                               |

|-----|----------|-------|-----------------------------------------------------------|

| D   | Released | 03/14 | Add DLA SMD #, change status to qualified                 |

| E   | Released | 04/14 | Add ESD rating                                            |

| F   | Released | 07/15 | Revise switching frequency limits and update format       |

| G   | Released | 08/15 | Remove reference to MSK5033                               |

| Н   | Released | 04/16 | Update specifications, clarification of application notes |

| J   | Released | 03/18 | Update to match manufacturer's specs                      |

| K   | Released | 04/18 | Update Programable Frequency Range upper bound Rset Value |

| L   | Released | 08/18 | Add Industrial Grade Temp Range and Thermal Resistance    |

| М   | Released | 03/22 | Remove MIL-PRF-38535, update company name and website     |

## TTM Technologies www.ttmtech.com

The information contained herein is believed to be accurate at the time of printing. TTM Technologies reserves the right to make changes to its products or specifications without notice, however and assumes no liability for the use of its products. Please visit our website for the most recent revision of this data sheet.